# Fujitsu Development Status and Some Topics towards Next MPI development

2015/06/23 Shinji Sumimoto Fujitsu Ltd.

## Topics

- Third Party Contribution Agreement StatusPRIMEHPC FX100 Overview

- Some Topics of Next MPI Library Development

# Third Party Contribution Agreement Status Fujitsu

- We are still working on internal negotiation process, because we have to apply new process including request for decision process.

- We need a couple of month to process. Sorry for late.

- After the internal negotiation process, Fujitsu will join the Open MPI Development Team.

- Soon... (I hope by the end of Sept.2015)

# **PRIMEHPC FX100 OVERVIEW**

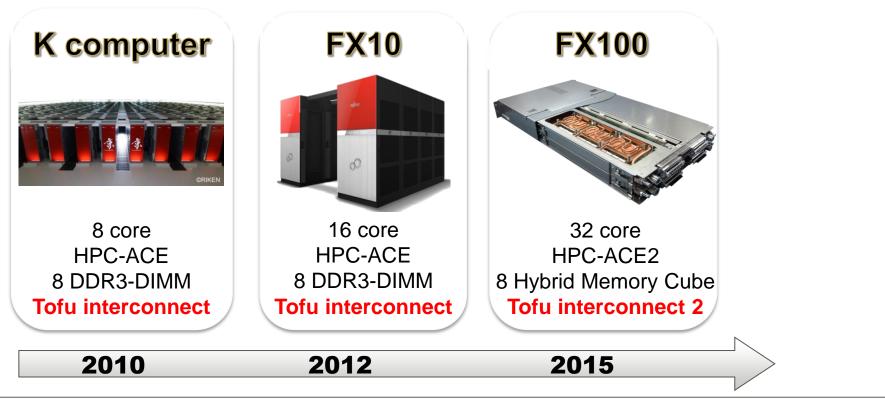

# K computer and Fujitsu PRIMEHPC series Fujitsu

- Massively parallel machines with single-socket per node

- Increased core-count and enhanced HPC instruction extension

- Eight memory channels for high throughput

- PRIMEHPC FX100 is the successor of FX10

- Realizing 100PFlops Class Post-Petascale Systems

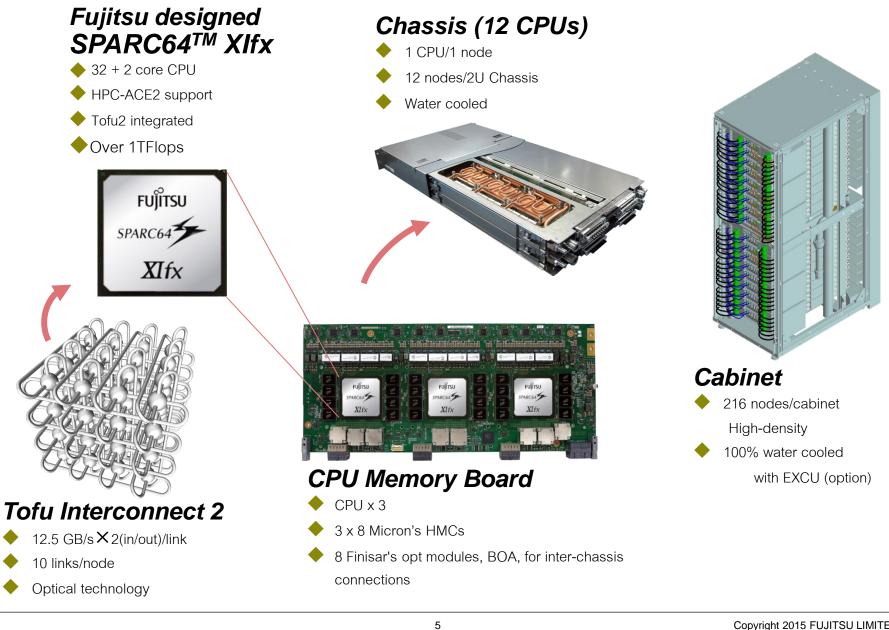

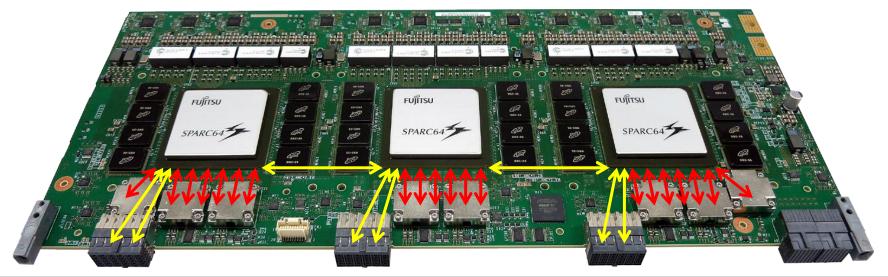

#### **PRIMEHPC FX100 Architecture**

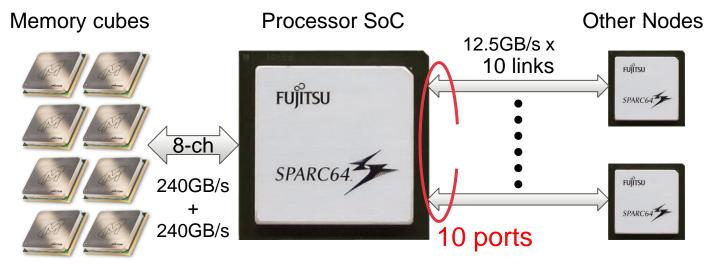

## PRIMEHPC FX100: System-on-Chip Integration Fujirsu

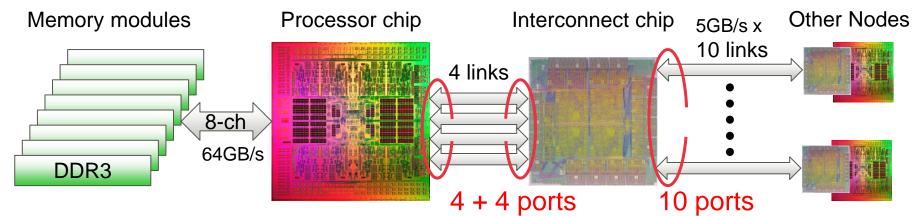

#### Tofu1 was implemented as a discrete chip

Tofu2 is integrated into a processor SoC

Number of link ports per node decreased from 18 to 10

### PRIMEHPC FX100: Transmission Technology

FUĴITSU

Link speed increases from 40 Gbps to 100 Gbps

Tofu1: 8 lanes × 6.25 Gbps × 8b/10b = 40 Gbps

Tofu2: 4 lanes × 25.78125 Gbps × 64b/66b = 100 Gbps

Number of lanes per node decreases from 144 to 40

2/3 of links uses optical transceivers

1 out of 3 nodes uses 6 optical links + 4 electrical links

2 out of 3 nodes use 7 optical links + 3 electrical links

# Some of Slides from SC14 ExaMPI Workshop Slides SOME TOPICS OF NEXT MPI LIBRARY DEVELOPMENT

## Issues of the Next Fujitsu MPI Libraries

- Higher Bandwidth and Lower Latency on many core systems

- Cache Injection for Lower Latency

- Single Core CPU Copy Performance Issue

- Memory Usage of MPI Library must be reduced dramatically

- Memory Saving Technologies of K computer is not enough: I talked the last OMPI Developer Meeting

- Better Power Consumption Saving

- Reducing Number of MPI Processing Instructions: Simplified MPI Architecture

# **PRIMEHPC FX100: Cache Injection**

#### Tofu2 supports Injecting received data into L2 cache directly

|                          | Tofu1        | Tofu2        |

|--------------------------|--------------|--------------|

| Memory bypass (sender)   | $\checkmark$ | $\checkmark$ |

| Memory bypass (receiver) |              | $\checkmark$ |

Injection flag On/Off is indicated by the sender

Communication latency is reduced by 0.16 usec

| Injection flag | Half round-trip latency |

|----------------|-------------------------|

| Off            | 0.87 usec               |

| On             | 0.71 usec               |

The evaluations used the Verilog RTL codes for the production

The estimated communication pattern is Ping-Pong of Put transfer

- Background of High Performance Communication on Many Core Processor for Exa-scale

- FUJITSU

- Communication Bandwidth of Interconnect continues to increase:

- Tofu(5+5)GB/s x 4  $\rightarrow$  Tofu2(12.5+12.5)GB/s x 4

- Multiple RDMA engines: 4 RDMAs on Tofu and Tofu2

- Single CPU Core Processing Frequency will not increase dramatically because of Power Wall

- This is because many core CPUs become to use widelyXeon Phi: around 1GHz, FX10: 1.8GHz

The problem is memory copy performance of single CPU core will not increase dramatically! Issues of Single Core Memory Copy Performance Limitation

#### Two Major Issues in case of Network Bandwidth >Single CPU Copy Bandwidth:

- Simple Intra-Node Communication

- Simple Communication such as MPI\_Send, MPI\_Recv

- Collective Communication especially handling multi-rail network

- Simple Communication such as MPI\_Bcast

- Communication with Arithmetic Computation such as MPI\_Reduce

Solution

- Hardware Offload: DMA Engine, Loopback Data Transfer

- Multi Threaded Communication Processing

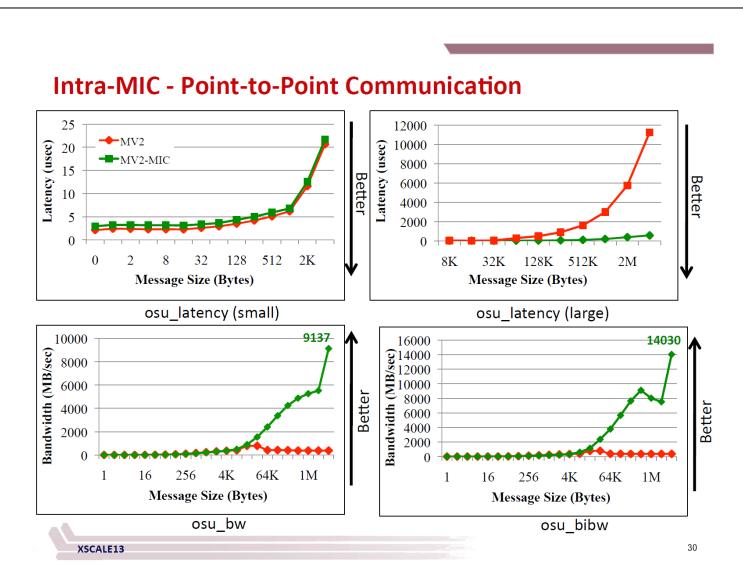

# Xeon-Phi Case: MVAPICH2-MIC

MVAPICH2-MIC: A High-Performance MPI Library for Xeon Phi Clusters with InfiniBand, by Sreeram Potluri at Extreme Scaling Workshop, August 2013.

> http://nowlab.cse.ohio-state.edu/publications/ conf-presentations/2013/Sreeram-XSCALE13.pdf

Approach:

Short Message Size: Using CPU Copy

Long Message Size: Using SCIF(DMA Engine)

#### Results:

- Pros: Simple Intra-Node Performance

- Cons: DMA engine Resource Bottleneck in case of number of processes Communication with Arithmetic Computation

- Multi Threaded Communication Processing will be needed

# Xeon Phi Case: MVAPICH2-MIC Solution

http://nowlab.cse.ohio-state.edu/publications/conf-presentations/2013/Sreeram-XSCALE13.pdf

# Xeon-Phi Case: MT-MPI

#### MT-MPI: Multithreaded MPI for Many-core Environments, Min-Si at ICS-14, June 2014

http://www.il.is.s.u-tokyo.ac.jp/~msi/pdf/ics2014-mtmpi.pdf

- Approach: Multi Threaded Communication Processing by OpenMP

- Derived Data Type Processing for Pack, Un-pack

- Shared Memory Communication for Long Messages

Results:

- Pros: Higher Performance

- Cons: Depending on number of Idle Threads

# MULTI-THREAD OPTIMIZATION IN MPI LIBRARIES

# Multi-Thread Optimization in MPI Libraries

- Assuming to Implement in MPI\_THREAD\_FUNNEL or MPI\_THREAD\_SERIALIZED Environment

- For Simple Intra-Node Communication

- Increasing Communication Performance by using Multi Threaded CPU Copy.

- For Development of Collective Communication especially Handling Multi-Rail Network

- For Simple Communication such as MPI\_Bcast

- Optimization by Multi-Threaded CPU Copies

- For Communication with Arithmetic Computation such as MPI\_Reduce

- Increasing Arithmetic Performance by using multi threads

# For General Optimization of Collective Communication

- Collective Communication In MPI\_THREAD\_MULTIPLE Environment

- Simple Implementation using MPI\_isend, MPI\_irecv for each rail in multi-rail network

- Realizing Portable Implementation

MPI\_Bcast by using Long-message algorithm: "Trinaryx3"

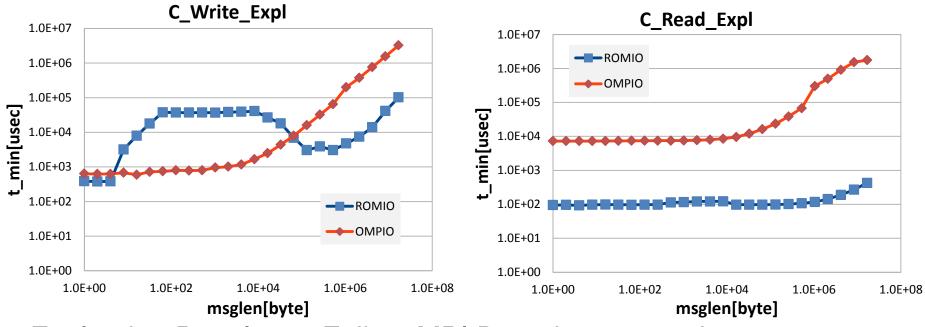

# EVALUATION OF MPI-IO OMPIO VS ROMIO

# **Evaluation Results Using IMB-IO**

- Evaluation Results on Fujitsu MPI Based on 1.8 series on PRIMEHPC FX10 384 nodes

- C\_Write\_Expl: Better Performance in Short Message

- C\_Read\_Exple: Worse Performance than ROMIO

- A lot of Debug Message in some benchmarks because of un-implemented functions

- We also evaluated using IOR, but IOR did not complete in OMPIO

# FUJTSU

shaping tomorrow with you