FIFO(First input First Output):先进先出,先写入的数据先读取

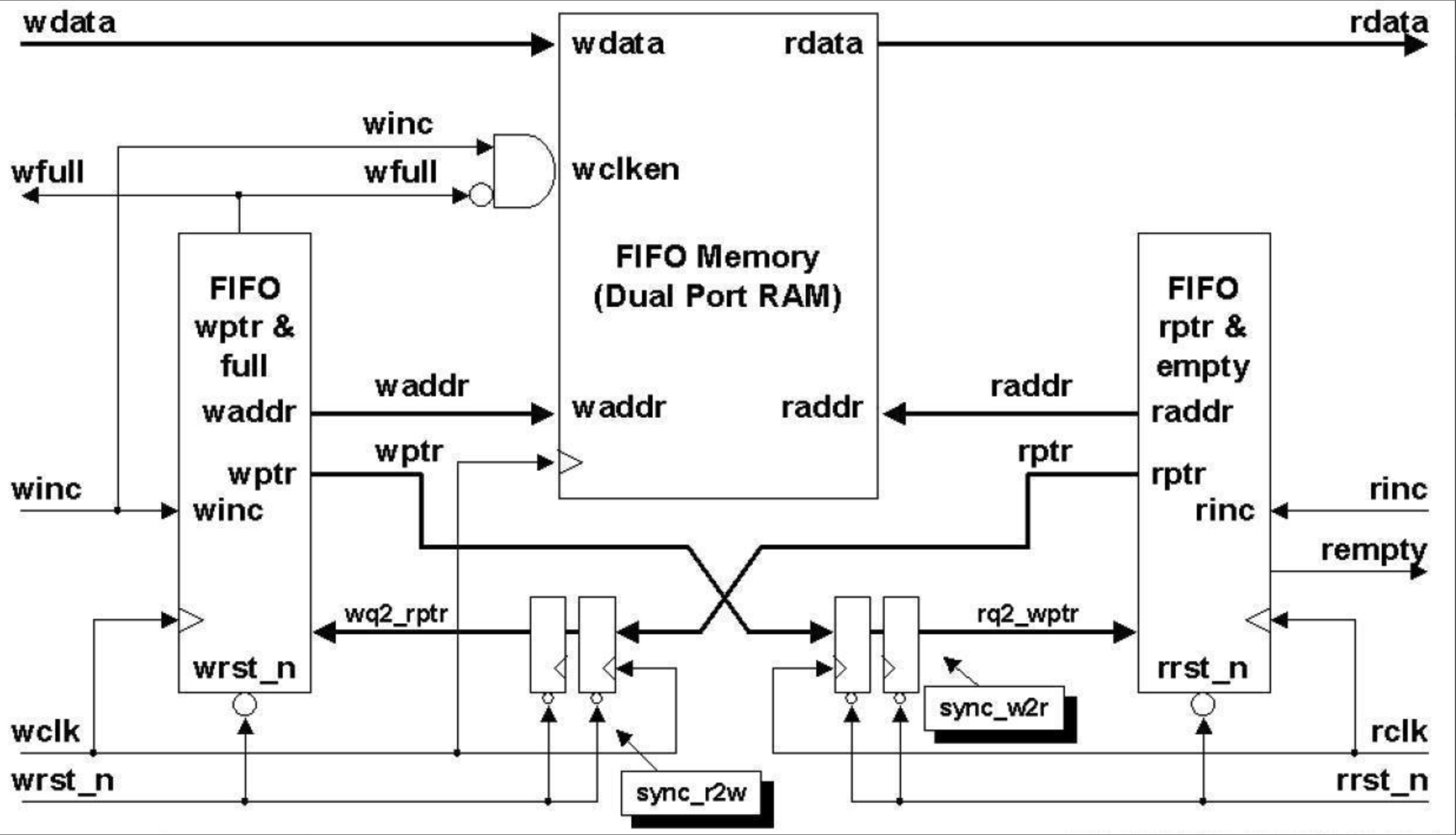

- FIFO写逻辑控制——产生FIFO写地址、写有效信号,同时产生FIFO写满、写错等状态信号;

- FIFO读逻辑控制——产生FIFO读地址、读有效信号,同时产生FIFO读空、读错等状态信号;

- 时钟同步逻辑——通过两级DFF分别将写时钟域的写指针同步到读时钟域,将读时钟域的读指针同步到写时钟域;

- 格雷码计数器——格雷码计数器中二进制计数器的低(n-1)位可以直接作为FIFO存储单元的地址指针;

- FIFO存储体(如Memory,reg等)。

因为这里读写用的是两个不同的时钟。这将涉及到跨时钟域问题。跨时钟域的电路会带来亚稳态。

关键挑战:如何避免读写指针跨时钟域传递时的亚稳态(Metastability),并准确判断FIFO的空/满状态。

格雷码(Gray Code):相邻数值仅有一位变化,减少跨时钟域同步时的错误概率。

指针同步:将写指针同步到读时钟域判断“空”,读指针同步到写时钟域判断“满”。

1.verilog

- 如果你有modelsim就可以clone本地后打开ancyfifo.mpf文件,即可看到所有的代码:

- 如果没有也可以选择下面的文件直接下载到本地,自己建立modelsim project(如果这里不理解需要你去学习如何使用modelsim)

Asynchronous-FIFO/

├─ fifo.v

├─ read_ctrl.v

├─ write_ctrl.v

├─ sync_gray.v

├─ dual_port_ram.v

├─ testbench.v